سوئچنگ پاور ریپل ناگزیر ہے۔ ہمارا حتمی مقصد آؤٹ پٹ ریپل کو قابل برداشت سطح تک کم کرنا ہے۔ اس مقصد کو حاصل کرنے کا سب سے بنیادی حل یہ ہے کہ لہروں کی نسل سے بچنا ہے۔ سب سے پہلے اور وجہ۔

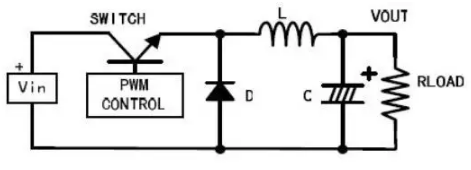

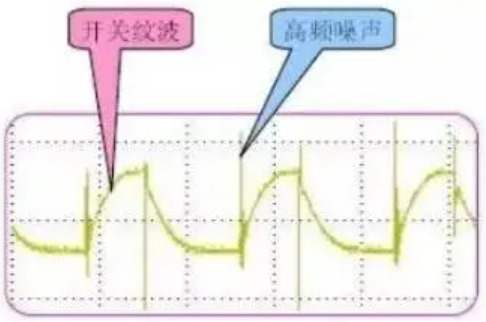

SWITCH کے سوئچ کے ساتھ، انڈکٹنس L میں کرنٹ بھی آؤٹ پٹ کرنٹ کی درست قدر پر اوپر اور نیچے اتار چڑھاؤ کرتا ہے۔ لہذا، وہاں ایک لہر بھی ہوگی جو آؤٹ پٹ کے آخر میں سوئچ جیسی فریکوئنسی ہے۔ عام طور پر، رائبر کی لہریں اس کا حوالہ دیتی ہیں، جس کا تعلق آؤٹ پٹ کیپسیٹر اور ESR کی صلاحیت سے ہے۔ اس لہر کی فریکوئنسی دسیوں سے سینکڑوں کلو ہرٹز کی حد کے ساتھ سوئچنگ پاور سپلائی کے برابر ہے۔

اس کے علاوہ، سوئچ عام طور پر بائی پولر ٹرانجسٹر یا MOSFETs کا استعمال کرتا ہے۔ اس سے کوئی فرق نہیں پڑتا ہے کہ کوئی بھی ہے، اس کے آن اور ڈیڈ ہونے پر عروج اور کمی کا وقت ہوگا۔ اس وقت، سرکٹ میں کوئی شور نہیں ہوگا جو سوئچ کے بڑھتے ہوئے گھٹنے کے وقت کے برابر ہے، یا چند بار، اور عام طور پر دسیوں میگاہرٹز ہے۔ اسی طرح، ڈایڈڈ ڈی ریورس ریکوری میں ہے. مساوی سرکٹ مزاحمتی کیپسیٹرز اور انڈکٹرز کی سیریز ہے، جو گونج پیدا کرے گا، اور شور کی فریکوئنسی دسیوں میگاہرٹز ہے۔ یہ دونوں شور عام طور پر ہائی فریکوئنسی شور کہلاتے ہیں، اور طول و عرض عام طور پر لہر سے بہت بڑا ہوتا ہے۔

اگر یہ ایک AC / DC کنورٹر ہے تو، اوپر کی دو لہروں (شور) کے علاوہ، AC شور بھی ہے۔ تعدد ان پٹ AC پاور سپلائی کی فریکوئنسی ہے، تقریباً 50-60Hz۔ ایک شریک موڈ شور بھی ہے، کیونکہ بہت سے سوئچنگ پاور سپلائی کا پاور ڈیوائس شیل کو ریڈی ایٹر کے طور پر استعمال کرتا ہے، جو ایک مساوی گنجائش پیدا کرتا ہے۔

سوئچنگ پاور ریپلز کی پیمائش

بنیادی ضروریات:

ایک آسیلوسکوپ AC کے ساتھ جوڑا

20MHz بینڈوتھ کی حد

تحقیقات کے زمینی تار کو ان پلگ کریں۔

1.AC کپلنگ سپرپوزیشن DC وولٹیج کو ہٹانا اور ایک درست ویوفارم حاصل کرنا ہے۔

2. 20MHz بینڈوتھ کی حد کو کھولنا ہائی فریکوئنسی شور کی مداخلت کو روکنے اور غلطی کو روکنے کے لیے ہے۔ چونکہ اعلی تعدد مرکب کا طول و عرض بڑا ہے، اس کی پیمائش کرتے وقت اسے ہٹا دیا جانا چاہئے۔

3. آسیلوسکوپ پروب کے گراؤنڈ کلپ کو ان پلگ کریں، اور مداخلت کو کم کرنے کے لیے زمینی پیمائش کی پیمائش کا استعمال کریں۔ بہت سے محکموں میں زمینی حلقے نہیں ہیں۔ لیکن یہ فیصلہ کرتے وقت اس عنصر پر غور کریں کہ آیا یہ اہل ہے یا نہیں۔

دوسرا نقطہ 50Ω ٹرمینل استعمال کرنا ہے۔ آسیلوسکوپ کی معلومات کے مطابق، 50Ω ماڈیول DC جزو کو ہٹانا اور AC جزو کی درست پیمائش کرنا ہے۔ تاہم، اس طرح کی خصوصی تحقیقات کے ساتھ چند آسیلوسکوپس موجود ہیں۔ زیادہ تر معاملات میں، 100kΩ سے 10MΩ تک تحقیقات کا استعمال کیا جاتا ہے، جو کہ عارضی طور پر غیر واضح ہے۔

سوئچنگ ریپل کی پیمائش کرتے وقت مندرجہ بالا بنیادی احتیاطی تدابیر ہیں۔ اگر آسیلوسکوپ پروب براہ راست آؤٹ پٹ پوائنٹ کے سامنے نہیں ہے، تو اسے بٹی ہوئی لائنوں یا 50Ω سماکشی کیبلز سے ناپا جانا چاہیے۔

ہائی فریکوئنسی شور کی پیمائش کرتے وقت، آسیلوسکوپ کا مکمل بینڈ عام طور پر سینکڑوں میگا سے گیگا ہرٹز کی سطح پر ہوتا ہے۔ دوسرے اوپر والے کی طرح ہیں۔ شاید مختلف کمپنیوں کے پاس ٹیسٹ کے مختلف طریقے ہیں۔ حتمی تجزیہ میں، آپ کو اپنے ٹیسٹ کے نتائج کا علم ہونا چاہیے۔

آسیلوسکوپ کے بارے میں:

کچھ ڈیجیٹل آسیلوسکوپ مداخلت اور اسٹوریج کی گہرائی کی وجہ سے لہروں کی صحیح پیمائش نہیں کر سکتے ہیں۔ اس وقت، آسیلوسکوپ کو تبدیل کیا جانا چاہئے. بعض اوقات اگرچہ پرانی سمولیشن آسیلوسکوپ بینڈوڈتھ صرف دسیوں میگا ہوتی ہے، لیکن کارکردگی ڈیجیٹل آسیلوسکوپ سے بہتر ہوتی ہے۔

سوئچنگ پاور ریپلز کی روک تھام

لہروں کو تبدیل کرنے کے لئے، نظریاتی طور پر اور اصل میں موجود ہیں. اسے دبانے یا کم کرنے کے تین طریقے ہیں:

1. انڈکٹنس اور آؤٹ پٹ کیپسیٹر فلٹرنگ میں اضافہ کریں۔

سوئچنگ پاور سپلائی کے فارمولے کے مطابق، انڈکٹو انڈکٹنس کی موجودہ اتار چڑھاؤ کا سائز اور انڈکٹنس ویلیو الٹا متناسب ہو جاتا ہے، اور آؤٹ پٹ ریپلز اور آؤٹ پٹ کیپسیٹرز الٹا متناسب ہوتے ہیں۔ لہذا، برقی اور آؤٹ پٹ کیپسیٹرز میں اضافہ لہروں کو کم کر سکتا ہے۔

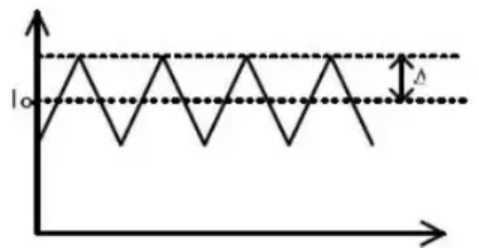

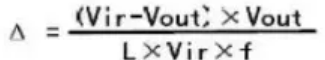

اوپر دی گئی تصویر سوئچنگ پاور سپلائی انڈکٹر L میں کرنٹ ویوفارم ہے۔ اس کا ریپل کرنٹ △ i درج ذیل فارمولے سے شمار کیا جا سکتا ہے:

یہ دیکھا جا سکتا ہے کہ ایل ویلیو میں اضافہ یا سوئچنگ فریکوئنسی میں اضافہ انڈکٹنس میں موجودہ اتار چڑھاو کو کم کر سکتا ہے۔

اسی طرح، آؤٹ پٹ ریپلز اور آؤٹ پٹ کیپسیٹرز کے درمیان تعلق: VRIPPLE = IMAX/(CO × F)۔ یہ دیکھا جا سکتا ہے کہ آؤٹ پٹ کیپسیٹر ویلیو میں اضافہ لہر کو کم کر سکتا ہے۔

عام طریقہ یہ ہے کہ بڑی صلاحیت کے مقصد کو حاصل کرنے کے لیے آؤٹ پٹ کیپیسیٹینس کے لیے ایلومینیم الیکٹرولائٹک کیپسیٹرز کا استعمال کیا جائے۔ تاہم، الیکٹرولائٹک کیپسیٹرز ہائی فریکوئنسی شور کو دبانے میں زیادہ موثر نہیں ہیں، اور ESR نسبتاً بڑا ہے، اس لیے یہ ایلومینیم الیکٹرولائٹک کیپسیٹرز کی کمی کو پورا کرنے کے لیے اس کے ساتھ ایک سیرامک کپیسیٹر کو جوڑ دے گا۔

ایک ہی وقت میں، جب بجلی کی فراہمی کام کر رہی ہوتی ہے، ان پٹ ٹرمینل کا وولٹیج VIN تبدیل نہیں ہوتا ہے، لیکن سوئچ کے ساتھ کرنٹ تبدیل ہوتا ہے۔ اس وقت، ان پٹ پاور سپلائی کرنٹ کنواں فراہم نہیں کرتی ہے، عام طور پر موجودہ ان پٹ ٹرمینل کے قریب (مثال کے طور پر بکس کی قسم کو لے کر، سوئچ کے قریب ہے)، اور کرنٹ فراہم کرنے کے لیے اہلیت کو جوڑتا ہے۔

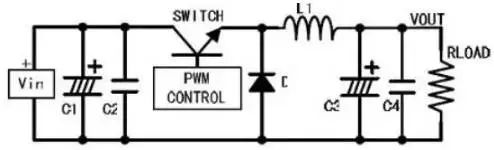

اس جوابی اقدام کو لاگو کرنے کے بعد، بک سوئچ پاور سپلائی نیچے دی گئی تصویر میں دکھائی گئی ہے۔

مذکورہ بالا نقطہ نظر لہروں کو کم کرنے تک محدود ہے۔ حجم کی حد کی وجہ سے، انڈکٹنس بہت بڑا نہیں ہوگا؛ آؤٹ پٹ کیپسیٹر ایک خاص حد تک بڑھ جاتا ہے، اور لہروں کو کم کرنے پر کوئی واضح اثر نہیں ہوتا ہے۔ سوئچنگ فریکوئنسی میں اضافہ سوئچ نقصان میں اضافہ کرے گا. لہٰذا جب ضروریات سخت ہوں تو یہ طریقہ بہت اچھا نہیں ہے۔

سوئچنگ پاور سپلائی کے اصولوں کے لیے، آپ مختلف قسم کے سوئچنگ پاور ڈیزائن مینوئل کا حوالہ دے سکتے ہیں۔

2. دو سطحی فلٹرنگ کا مقصد پہلے درجے کے ایل سی فلٹرز کو شامل کرنا ہے۔

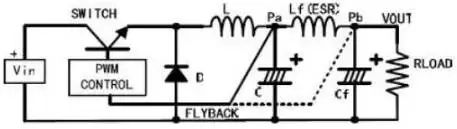

شور کی لہر پر LC فلٹر کا روکنے والا اثر نسبتاً واضح ہے۔ ہٹائی جانے والی لہر کی فریکوئنسی کے مطابق، فلٹر سرکٹ بنانے کے لیے مناسب انڈکٹر کیپسیٹر کا انتخاب کریں۔ عام طور پر، یہ لہروں کو اچھی طرح سے کم کر سکتا ہے۔ اس صورت میں، آپ کو فیڈ بیک وولٹیج کے سیمپلنگ پوائنٹ پر غور کرنے کی ضرورت ہے۔ (جیسا کہ نیچے دکھایا گیا ہے)

سیمپلنگ پوائنٹ کا انتخاب LC فلٹر (PA) سے پہلے کیا جاتا ہے، اور آؤٹ پٹ وولٹیج کم ہو جائے گا۔ کیونکہ کسی بھی انڈکٹنس میں ڈی سی مزاحمت ہوتی ہے، جب کرنٹ آؤٹ پٹ ہوتا ہے، تو انڈکٹنس میں وولٹیج ڈراپ ہوتا ہے، جس کے نتیجے میں پاور سپلائی کے آؤٹ پٹ وولٹیج میں کمی واقع ہوتی ہے۔ اور یہ وولٹیج ڈراپ آؤٹ پٹ کرنٹ کے ساتھ بدل جاتا ہے۔

سیمپلنگ پوائنٹ کا انتخاب LC فلٹر (PB) کے بعد کیا جاتا ہے، تاکہ آؤٹ پٹ وولٹیج وہی وولٹیج ہو جو ہم چاہتے ہیں۔ تاہم، پاور سسٹم کے اندر ایک انڈکٹنس اور ایک کپیسیٹر متعارف کرایا جاتا ہے، جو سسٹم میں عدم استحکام کا سبب بن سکتا ہے۔

3. سوئچنگ پاور سپلائی کے آؤٹ پٹ کے بعد، LDO فلٹرنگ کو جوڑیں۔

لہروں اور شور کو کم کرنے کا یہ سب سے مؤثر طریقہ ہے۔ آؤٹ پٹ وولٹیج مستقل ہے اور اسے اصل فیڈ بیک سسٹم کو تبدیل کرنے کی ضرورت نہیں ہے، لیکن یہ سب سے زیادہ لاگت سے موثر اور سب سے زیادہ بجلی کی کھپت بھی ہے۔

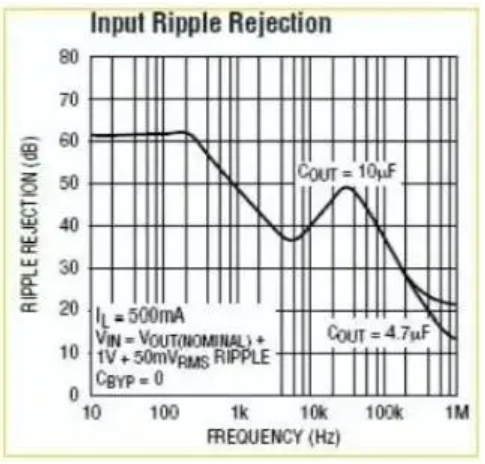

کسی بھی LDO کا ایک اشارے ہوتا ہے: شور دبانے کا تناسب۔ یہ ایک فریکوئنسی-DB وکر ہے، جیسا کہ نیچے دی گئی تصویر میں دکھایا گیا ہے LT3024 LT3024 کا وکر ہے۔

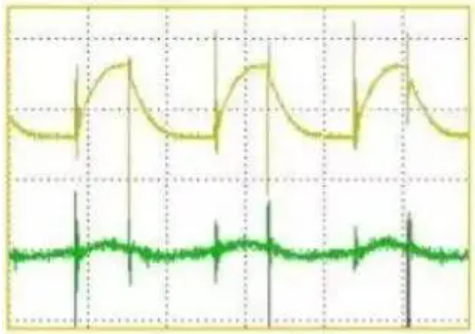

LDO کے بعد، سوئچنگ ریپل عام طور پر 10mV سے نیچے ہوتی ہے۔ مندرجہ ذیل اعداد و شمار LDO سے پہلے اور بعد کی لہروں کا موازنہ ہے:

اوپر کے اعداد و شمار کے منحنی خطوط اور بائیں جانب موج کے مقابلے میں، یہ دیکھا جا سکتا ہے کہ LDO کا روکنے والا اثر سینکڑوں KHz کی سوئچنگ لہروں کے لیے بہت اچھا ہے۔ لیکن اعلی تعدد کی حد کے اندر، LDO کا اثر اتنا مثالی نہیں ہے۔

لہروں کو کم کریں۔ سوئچنگ پاور سپلائی کی پی سی بی وائرنگ بھی اہم ہے۔ اعلی تعدد شور کے لئے، اعلی تعدد کی بڑی تعدد کی وجہ سے، اگرچہ پوسٹ اسٹیج فلٹرنگ کا ایک خاص اثر ہے، اثر واضح نہیں ہے. اس سلسلے میں خصوصی مطالعات موجود ہیں۔ سادہ طریقہ یہ ہے کہ ڈائیوڈ اور کپیسیٹینس C یا RC پر ہو، یا انڈکٹینس کو سیریز میں جوڑیں۔

مندرجہ بالا اعداد و شمار اصل ڈایڈڈ کا ایک مساوی سرکٹ ہے۔ جب ڈایڈڈ تیز رفتار ہو تو پرجیوی پیرامیٹرز پر غور کیا جانا چاہیے۔ ڈایڈڈ کی ریورس ریکوری کے دوران، مساوی انڈکٹینس اور مساوی کیپیسیٹینس ایک RC آسکیلیٹر بن گیا، جس سے ہائی فریکوئنسی دولن پیدا ہوتا ہے۔ اس ہائی فریکوئنسی دولن کو دبانے کے لیے، ڈایڈڈ کے دونوں سروں پر کپیسیٹینس C یا RC بفر نیٹ ورک کو جوڑنا ضروری ہے۔ مزاحمت عام طور پر 10Ω-100 ω ہے، اور گنجائش 4.7PF-2.2NF ہے۔

ڈایڈڈ C یا RC پر کیپیسیٹینس C یا RC کا تعین بار بار ٹیسٹ کے ذریعے کیا جا سکتا ہے۔ اگر اسے صحیح طریقے سے منتخب نہیں کیا گیا ہے، تو یہ زیادہ شدید دولن کا سبب بنے گا۔

پوسٹ ٹائم: جولائی 08-2023